The IO devices connected to a microcomputer system provides an efficient means of communication between the microcomputer system and the outside world. These IO devices are commonly called peripherals and include Keyboards, CRT display, Printerns, hard disk, etc.

Since the characteristic of the IO devices are not compitable with that of the microprocessor, interface hardware circuitry between the microprocessor and I/o devices are necessary.

There are three major types of data transfer between the microcomputer and an IO device. They are as follows.

- 1) Programmed IO data transfer

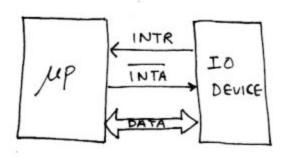

- 2) Intersupt IO data transfer

- 3) Direct memory access (DMA).

Prepared by: Prof. Md Isteyaque Ashraf Guest Faculty, Dep"t of ECE PCE, Purnea

Programmed IO data transfer: It is of two types: a) synchronous b) Asynchronous

- a) <u>Synchronous</u>: When the speed of IO devices is compatible to CPU, Synchronous type of data transfer can be achieved In this mode the status of the device is not checked before undertaking any data transfer, that means, the device is arsumed to be ready when the data transfer takes place. This is the simplest scheme and requires minimum hardware/software to implement.

- b) Asynchronous: In this mode of data transfer the CPU has to check the status of the IO devices for the availability of the data to be transferred, whether IO device is free to accept the data from the CPU. This mode is used when the speed of the IO device is slower than CPU. hame "handshake I/O".

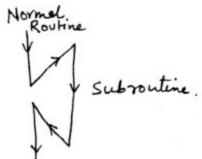

This mode is used for data transfer with slow peripheral and also when the occurrence of data is unpredictable in nature. In this method data transfer is achieved by intersupting the microprocessor by the device. When the device is ready for data transfer, it sends an interrupt request signed to the microprocessor, the microprocessor then sends an interrupt acknowledge signal to the IO device indicating that it has received the request and suspends its job after completing its current instruction, it saves the current address and status and execute the ISS (Interrupt service Subroutine).

DIRECT MEMORY ACCESS (DMA)

Q. What is DMA?

Prepared by: Prof. Md Isteyaque Ashraf Guest Faculty,Dep"t of ECE PCE,Purnea

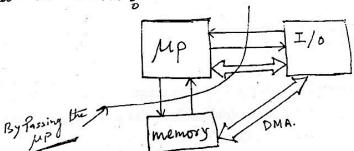

Either in Programmed I/o or interrupt I/o, the data transfer between I/o and external memory is Via the Accumulator, for Voluminous(huge) / Large data transfer this method are time lonsuning and uneconomical even though the I/o devices speed matches with the speed of NP. In Such Situation it is advisable to Provide facilities for transfer of data directly between I/o and the external memory without going through the Accumulator. DMA is a special type of I/o technique used for high speed data transfer between System memory and Peripherals, by Parring the MP. Explain the function of HOLD & HLDA Pins of 8085

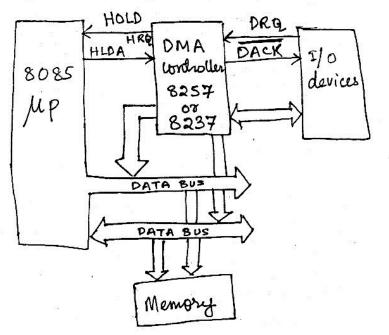

HOLD: This is Active high Lignal from DMA controller to 8085 µp. This Signal indicates that the DMA controller is requesting the use of the address and data bus of 8085.

<u>HLDA</u>: This is Active high Signal from UP to the DMA controller After receiving the HOLD Signal from the DMA controller UP releases its address and data bees and generates HLDA for the DMA controller.

Explain the following term / Signal :-

SLAVE MODE & MASTER MODE: - During the DMA Process, Initially the DMA chip (8237 or 8257) is slave and 8085 master, 8085 loads with words, count value to DMA chip, then UP releases HLDA, then it give the control of all data bees to DMA and now the DMA chip acts as a Moster, and now the DMA chip will access the data bees, after end of Programme it sends signal to UP and the order is reversed.

DACK :- Direct memory access acknowledge. HRQ :- Hold Request.

DRQ :- Direct memory excess sequest.

It is bent by I/O to DMA controller, then the DMA controller Sends Signal HRQ which is connected to the HOLD Pin of 8035, after receiving HOLD UP Sends HLDA, this means UP releases the control of data bus and now the DMA controller Sends DACK to 2/O devices, now the I/O device Starts to transfer data from the memory.

3

Discuss the steps for data transfer process between a floppy disk and R/W memory of 8085 System using DMA.

The Process of data transfer between the system memory and Peripheral under DMA controller can be classified between two mode.

1 SLAVE MODE: - In this mode the DMA controller is treated as a Peripheral using following steps: (a) The MPU selects DMA controller through chip select (cs) line

- (b) The MPU writes the control word in channel register and command/status register by using at control signal IOW and IOR.

- 2 MASTER, MODE : After the Initialization, the 8237 in mastermode keeps checking for a DMA request and the steps in data transfer can be disted as follows:

- (a) when the Peripheral is ready for data transfer it sends an active high signal to DRQ line of 8257.

(D) After receiving the DRQ signal 8257 generates an active high HRQ (Hold Request) signal which is connected to HOLD Pin & 8085.

- (C) After receiving HOLD signal the UP releases its Buses and Sends the HLDA (Hold acknowledge signal) to 8257.

- (d) After seceiving the HLDA signal from UP the DMA controller sends DACK to the Peripheral.

- @ Peripheral places it's data on the buses and starts data transfer between Peripheral and System memory.

- (f) At the end of data transfer the DMA controller generates EOP (end of Process) to inform the Perpheral that data transfer is complete.